मल्टी-लेयर पीसीबी डिझाइन करताना EMI समस्या कशी सोडवायची हे तुम्हाला माहिती आहे का?

मला सांगू द्या!

ईएमआय समस्या सोडवण्याचे अनेक मार्ग आहेत.आधुनिक EMI सप्रेशन पद्धतींमध्ये हे समाविष्ट आहे: EMI सप्रेशन कोटिंग वापरणे, योग्य EMI सप्रेशन भाग निवडणे आणि EMI सिम्युलेशन डिझाइन.सर्वात मूलभूत PCB लेआउटवर आधारित, हा पेपर EMI रेडिएशन आणि PCB डिझाइन कौशल्य नियंत्रित करण्यासाठी PCB स्टॅकच्या कार्यावर चर्चा करतो.

पॉवर बस

IC च्या पॉवर पिनजवळ योग्य कॅपेसिटन्स ठेवून IC च्या आउटपुट व्होल्टेज जंपला गती दिली जाऊ शकते.तथापि, या समस्येचा शेवट नाही.कॅपेसिटरच्या मर्यादित फ्रिक्वेंसी प्रतिसादामुळे, कॅपेसिटरला पूर्ण वारंवारता बँडमध्ये IC आउटपुट स्वच्छपणे चालविण्यासाठी आवश्यक हार्मोनिक शक्ती निर्माण करणे अशक्य आहे.याव्यतिरिक्त, पॉवर बसवर तयार झालेल्या क्षणिक व्होल्टेजमुळे डीकपलिंग मार्गाच्या इंडक्टन्सच्या दोन्ही टोकांना व्होल्टेज ड्रॉप होईल.हे क्षणिक व्होल्टेज हे मुख्य सामान्य मोड EMI हस्तक्षेप स्त्रोत आहेत.आपण या समस्या कशा सोडवू शकतो?

आमच्या सर्किट बोर्डवरील IC च्या बाबतीत, IC च्या सभोवतालचा पॉवर लेयर हा एक चांगला उच्च-फ्रिक्वेंसी कॅपेसिटर म्हणून ओळखला जाऊ शकतो, जो स्वच्छ आउटपुटसाठी उच्च-फ्रिक्वेंसी ऊर्जा प्रदान करणार्या वेगळ्या कॅपेसिटरद्वारे गळती होणारी ऊर्जा गोळा करू शकतो.याव्यतिरिक्त, चांगल्या पॉवर लेयरची इंडक्टन्स लहान असते, त्यामुळे इंडक्टरद्वारे संश्लेषित केलेले क्षणिक सिग्नल देखील लहान असते, त्यामुळे सामान्य मोड EMI कमी होतो.

अर्थात, पॉवर सप्लाय लेयर आणि आयसी पॉवर सप्लाय पिन यांच्यातील कनेक्शन शक्य तितके लहान असणे आवश्यक आहे, कारण डिजिटल सिग्नलची वाढणारी किनार अधिक वेगवान आणि वेगवान आहे.आयसी पॉवर पिन असलेल्या पॅडशी थेट कनेक्ट करणे चांगले आहे, ज्यावर स्वतंत्रपणे चर्चा करणे आवश्यक आहे.

कॉमन मोड EMI नियंत्रित करण्यासाठी, पॉवर लेयर डिकपल होण्यासाठी आणि पुरेशी कमी इंडक्टन्स असण्यासाठी पॉवर लेयरची चांगली डिझाइन केलेली जोडी असणे आवश्यक आहे.काही लोक विचारतील, ते किती चांगले आहे?उत्तर पॉवर लेयर, लेयर्समधील सामग्री आणि ऑपरेटिंग फ्रिक्वेंसी (म्हणजे, IC उदय वेळेचे कार्य) यावर अवलंबून असते.सर्वसाधारणपणे, पॉवर लेयरमधील अंतर 6mil आहे आणि इंटरलेअर FR4 मटेरियल आहे, त्यामुळे पॉवर लेयरच्या प्रति चौरस इंच समतुल्य कॅपॅसिटन्स सुमारे 75pF आहे.अर्थात, लेयरमधील अंतर जितके लहान असेल तितके कॅपॅसिटन्स मोठे असेल.

100-300ps च्या वाढीची वेळ असलेली अनेक उपकरणे नाहीत, परंतु IC च्या सध्याच्या विकास दरानुसार, 100-300ps च्या श्रेणीतील वाढ वेळ असलेली उपकरणे उच्च प्रमाणात व्यापतील.100 ते 300 PS वाढीच्या वेळेसह सर्किटसाठी, 3 मिलि लेयर स्पेसिंग यापुढे बहुतेक अनुप्रयोगांसाठी लागू होणार नाही.त्या वेळी, इंटरलेअर अंतर 1mil पेक्षा कमी असलेले डिलामिनेशन तंत्रज्ञान स्वीकारणे आणि उच्च डायलेक्ट्रिक स्थिरांक असलेल्या सामग्रीसह FR4 डायलेक्ट्रिक सामग्री बदलणे आवश्यक आहे.आता, सिरॅमिक्स आणि भांडी असलेले प्लास्टिक 100 ते 300ps राइज टाइम सर्किटच्या डिझाइन आवश्यकता पूर्ण करू शकतात.

जरी भविष्यात नवीन साहित्य आणि पद्धती वापरल्या जाऊ शकतात, सामान्य 1 ते 3 एनएस राइज टाइम सर्किट्स, 3 ते 6 मिलि लेयर स्पेसिंग आणि FR4 डायलेक्ट्रिक सामग्री सामान्यतः उच्च-श्रेणी हार्मोनिक्स हाताळण्यासाठी आणि क्षणिक सिग्नल पुरेसे कमी करण्यासाठी पुरेसे असतात, म्हणजे , कॉमन मोड ईएमआय खूप कमी केला जाऊ शकतो.या पेपरमध्ये, PCB लेयर्ड स्टॅकिंगचे डिझाइन उदाहरण दिले आहे, आणि लेयर स्पेसिंग 3 ते 6 mil असे गृहीत धरले आहे.

इलेक्ट्रोमॅग्नेटिक शिल्डिंग

सिग्नल राउटिंगच्या दृष्टिकोनातून, एक चांगली लेयरिंग स्ट्रॅटेजी म्हणजे सर्व सिग्नल ट्रेस एक किंवा अधिक लेयर्समध्ये ठेवणे, जे पॉवर लेयर किंवा ग्राउंड प्लेनच्या पुढे आहेत.वीज पुरवठ्यासाठी, एक चांगली लेयरिंग स्ट्रॅटेजी अशी असावी की पॉवर लेयर ग्राउंड प्लेनला लागून असेल आणि पॉवर लेयर आणि ग्राउंड प्लेनमधील अंतर शक्य तितके कमी असावे, ज्याला आपण "लेयरिंग" धोरण म्हणतो.

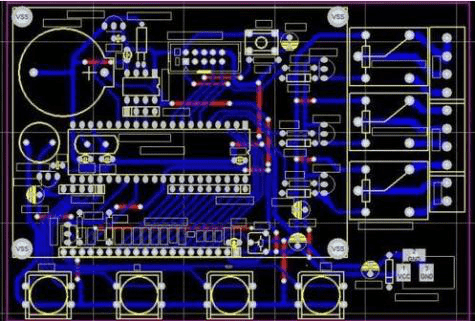

पीसीबी स्टॅक

कोणत्या प्रकारची स्टॅकिंग स्ट्रॅटेजी ईएमआयला संरक्षण आणि दडपण्यात मदत करू शकते?खालील स्तरित स्टॅकिंग योजना असे गृहीत धरते की वीज पुरवठा करंट एकाच स्तरावर वाहतो आणि एकाच स्तराच्या वेगवेगळ्या भागांमध्ये एकल व्होल्टेज किंवा अनेक व्होल्टेज वितरीत केले जातात.एकाधिक पॉवर लेयर्सच्या बाबतीत नंतर चर्चा केली जाईल.

4-प्लाय प्लेट

4-प्लाय लॅमिनेटच्या डिझाइनमध्ये काही संभाव्य समस्या आहेत.सर्व प्रथम, जरी सिग्नल लेयर बाहेरील लेयरमध्ये असेल आणि पॉवर आणि ग्राउंड प्लेन आतील लेयरमध्ये असले तरीही, पॉवर लेयर आणि ग्राउंड प्लेनमधील अंतर अजूनही खूप मोठे आहे.

जर खर्चाची आवश्यकता पहिली असेल तर, पारंपारिक 4-प्लाय बोर्डसाठी खालील दोन पर्यायांचा विचार केला जाऊ शकतो.ते दोघेही EMI सप्रेशन कार्यप्रदर्शन सुधारू शकतात, परंतु ते फक्त अशा प्रकरणांसाठी योग्य आहेत जेथे बोर्डवरील घटकांची घनता पुरेशी कमी आहे आणि घटकांभोवती पुरेसे क्षेत्र आहे (वीज पुरवठ्यासाठी आवश्यक तांबे कोटिंग ठेवण्यासाठी).

पहिली पसंतीची योजना आहे.PCB चे बाह्य स्तर सर्व स्तर आहेत, आणि मधले दोन स्तर सिग्नल / पॉवर स्तर आहेत.सिग्नल लेयरवरील वीज पुरवठा रुंद रेषांनी मार्गस्थ केला जातो, ज्यामुळे विद्युत पुरवठा करंटचा मार्ग कमी होतो आणि सिग्नल मायक्रोस्ट्रिप मार्गाचा अडथळा कमी होतो.EMI नियंत्रणाच्या दृष्टीकोनातून, ही उपलब्ध सर्वोत्तम 4-लेयर PCB रचना आहे.दुस-या योजनेत, बाह्य स्तर शक्ती आणि जमीन वाहून नेतो आणि मधला दोन स्तर सिग्नल वाहून नेतो.पारंपारिक 4-लेयर बोर्डच्या तुलनेत, या योजनेची सुधारणा लहान आहे आणि इंटरलेअर प्रतिबाधा पारंपारिक 4-लेयर बोर्डच्या तुलनेत चांगली नाही.

वायरिंगचा प्रतिबाधा नियंत्रित करायचा असल्यास, वरील स्टॅकिंग योजना वीज पुरवठा आणि ग्राउंडिंगच्या तांब्याच्या बेटाखाली वायरिंग घालण्यासाठी अत्यंत सावधगिरी बाळगली पाहिजे.याव्यतिरिक्त, डीसी आणि कमी वारंवारता दरम्यान कनेक्टिव्हिटी सुनिश्चित करण्यासाठी वीज पुरवठा किंवा स्ट्रॅटमवरील तांबे बेट शक्य तितके एकमेकांशी जोडलेले असावे.

6-प्लाय प्लेट

4-लेयर बोर्डवरील घटकांची घनता मोठी असल्यास, 6-लेयर प्लेट अधिक चांगले आहे.तथापि, 6-लेयर बोर्डच्या डिझाईनमध्ये काही स्टॅकिंग योजनांचा शील्डिंग प्रभाव पुरेसा चांगला नाही आणि पॉवर बसचा क्षणिक सिग्नल कमी होत नाही.दोन उदाहरणे खाली चर्चा केली आहेत.

पहिल्या प्रकरणात, वीज पुरवठा आणि ग्राउंड अनुक्रमे दुसऱ्या आणि पाचव्या स्तरांमध्ये ठेवलेले आहेत.कॉपर क्लेड पॉवर सप्लायच्या उच्च प्रतिबाधामुळे, सामान्य मोड ईएमआय रेडिएशन नियंत्रित करणे अत्यंत प्रतिकूल आहे.तथापि, सिग्नल प्रतिबाधा नियंत्रणाच्या दृष्टिकोनातून, ही पद्धत अगदी योग्य आहे.

दुसऱ्या उदाहरणात, वीज पुरवठा आणि ग्राउंड अनुक्रमे तिसऱ्या आणि चौथ्या स्तरांमध्ये ठेवलेले आहेत.हे डिझाइन वीज पुरवठ्याच्या तांबे क्लेड प्रतिबाधाची समस्या सोडवते.लेयर 1 आणि लेयर 6 च्या खराब इलेक्ट्रोमॅग्नेटिक शील्डिंग कार्यक्षमतेमुळे, विभेदक मोड EMI वाढतो.जर दोन बाह्य स्तरांवरील सिग्नल लाईन्सची संख्या कमी असेल आणि रेषांची लांबी खूपच लहान असेल (सिग्नलच्या सर्वोच्च हार्मोनिक तरंगलांबीच्या 1/20 पेक्षा कमी), तर डिझाइन डिफरेंशियल मोड EMI ची समस्या सोडवू शकते.परिणाम दर्शविते की विभेदक मोड EMI चे सप्रेशन विशेषतः चांगले असते जेव्हा बाहेरील थर तांब्याने भरलेला असतो आणि तांब्याने झाकलेले क्षेत्र ग्राउंड केलेले असते (प्रत्येक 1/20 तरंगलांबी अंतराल).वर नमूद केल्याप्रमाणे, तांबे घालणे आवश्यक आहे

पोस्ट वेळ: जुलै-29-2020